过去几十年,在摩尔定律的指导下,芯片中的晶体管数量大约每两年翻一番。晶体管的微缩技术革新增加了晶体管的密度。摩尔定律在20世纪60年代首次被发现,并一直延续到2010年代,至此以后,晶体管密度的发展开始放缓。如今,主流芯片包含了数十亿个晶体管,但如果摩尔定律能够继续按照当时的速度发展下去,它们的晶体管数量将是现在的15倍。

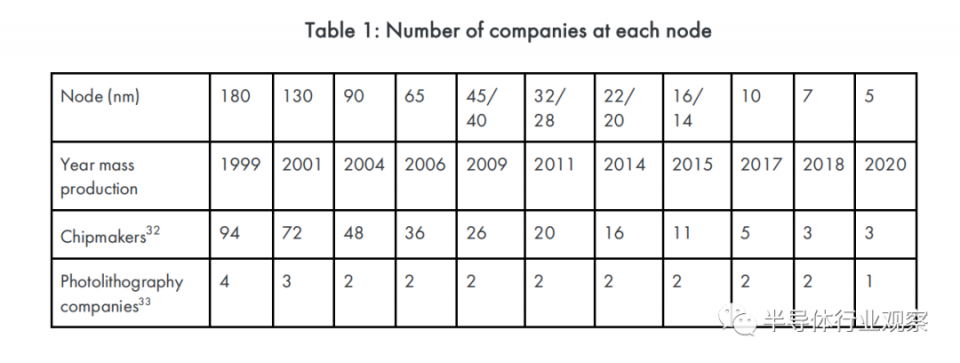

每一代晶体管密度的增加,被称为“节点”。每个节点对应于晶体管的大小(以长度表示),允许晶体管密度相对于前一个节点增加一倍。晶圆厂在2019年开始“风险生产”,即进行最新的5纳米节点(“nm”)的实验生产,预计在2020年实现量产,之前领先的节点是7纳米和10纳米。

伴随着摩尔定律衍生出来的是,由于较小的晶体管通常比较大的晶体管消耗更少的功率,所以随着晶体管密度的增加,单位芯片面积的功耗保持恒定。但是,晶体管的功耗降低速度在2007年左右有所放缓。

效率和速度的改进

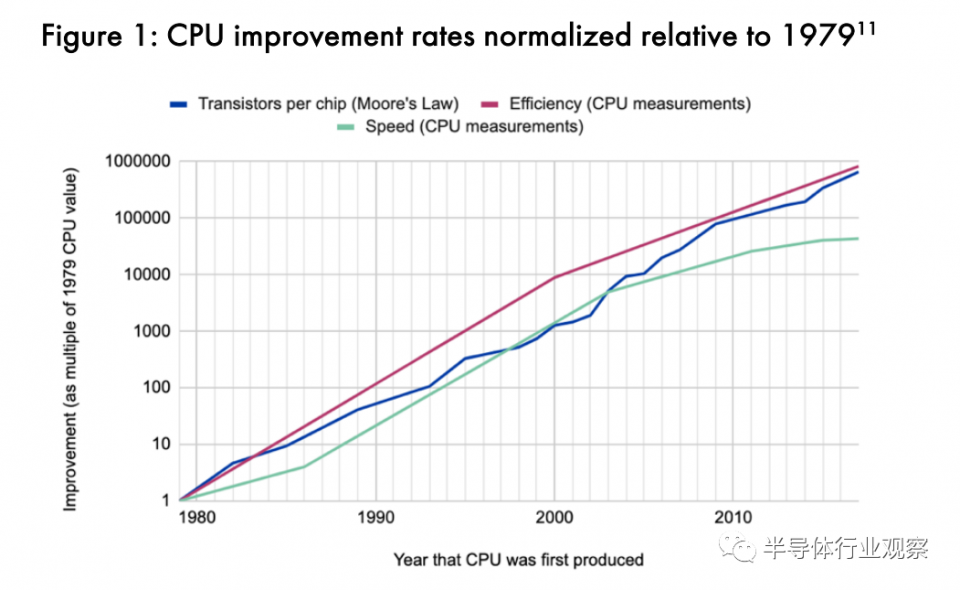

遵循着摩尔定律的发展,自1960年代以来,CPU速度已大大提高。较大的晶体管密度主要通过“频率缩放”来提高速度,即,晶体管在1和0之间切换更快,以允许给定执行单元在每秒内进行更多计算。由于较小的晶体管比较大的晶体管消耗的功率少,因此可以在不增加总功耗的情况下,提高晶体管的开关速度。图1显示了自1979年以来晶体管在密度,速度和效率方面的提高。

从1978年到1986年,频率变化每年使速度增加22%。然后,从1986年到2003年,由于频率扩展和设计的改进,使得并行计算得以实现,此时,计算速度以每年52%的速度增长。但随着频率扩展变慢,多核设计支持的并行性在2003年到2011年之间只能提供23%的年加速。利用可用CPU并行度的最后剩余部分,在2011年到2015年之间带来了12%的年提速,之后CPU速度的增长速度放缓至每年仅增加3%。

效率也大大提高了由于晶体管尺寸的减小降低了每个晶体管的功耗,在2000年之前,芯片峰值使用期间的整体CPU效率每1.57年翻一番。从那以后,由于晶体管功率降低的速度减慢,效率每2.6年才提高一倍,相当于每年仅提高30%的效率。

图1 增加晶体管密度可以提高效率和速度

随着晶体管的缩小和密度的增加,使得新的芯片设计成为可能,同时,也进一步提高了效率和速度。首先,CPU可以针对不同功能,优化的更多不同类型的执行单元。其次,更多的片内存储器可以减少对访问较慢的片外存储器的需要。诸如DRAM芯片之类的存储芯片同样可以集成更多的内存。第三,与串行计算的体系架构相比,CPU可以为实现并行计算提供更多的空间。同时,如果增加晶体管密度可以使CPU更小,那么一个设备当中就可以包含多个CPU(也称为多个“核”),而每个CPU可以同时运行不同的计算。

在20世纪90年代,因为芯片设计公司很难通过快速增加晶体管的可用性来开发设计可能性,因而,设计改进往往落后于晶体管密度的改进。为了克服这一瓶颈,设计公司相对更关注相对落后的节点,将大量芯片设计的制造工作外包给国外的低薪工程师,重复使用以前设计的部分(“IP核心”),并使用EDA软件将高级抽象设计转化为具体的晶体管级设计。

晶体管设计已达到基本尺寸限制

晶体管微缩到只有几个原子厚的尺寸,它们正迅速接近物理极限。适用于小尺寸的物理问题也使得晶体管在进行进一步的收缩时更具挑战性。第一个重大变化出现在21世纪初,当时晶体管的绝缘层变得非常薄,以至于电流开始从绝缘层上漏出。对此,工程师使用了更多的新型绝缘材料,即使其他组件继续收缩,绝缘层也不再收缩。

而后,晶体管又进行了更剧烈的结构变化。从20世纪60年代到2011年,晶体管都是一层一层叠放在一起制造的。然而,即使是更绝缘的材料也不能防止漏电。因此,工程师将更复杂的三维结构代替了这种平面布置。从2011年发布的22nm节点到当前的5 nm节点,这种新结构一直占据主导地位。但是,由5nm继续向下发展时,即使这种结构也会出现漏电的情况。因此,工程师为未来的3nm节点开发了一种全新的结构。它是由几个原子组成的,进一步减小了晶体管的厚度,使得先进工艺向3nm发展成为了可能。

今天,CPU的不断进步和领先于专用芯片的趋势正在走向终结。技术难题正在以比半导体市场增长更快的速度增加摩尔定律改进的成本。最终,这些经济和技术因素表明,实际晶体管密度将进一步落后于摩尔定律所预测的水平,并且我们可能会面临晶体管密度没有进一步得到显着改善的挑战。

晶体管开关速度的不断提高和晶体管功耗的降低使CPU优于专用芯片。在通用芯片占主导地位的时代,专用芯片无法产生足够的销售量来弥补高昂的设计成本。专用芯片的成本高昂,是因为专用芯片从设计上就是在针对CPU的特定任务进行改进。当快速的频率缩放仍可带来巨大的速度和效率优势时,专用CPU的运算能力很快就被下一代CPU所抵消,下一代CPU的成本分散在数百万个芯片的销售中。如今,摩尔定律的放慢意味着CPU不能再像以前那样进行迅速迭代。在这种情况下,专用芯片的使用寿命得以延长,使其更具经济效益。

成本的增长速度快于半导体市场

在细节上的技术困难不断增加,推高了整个供应链的高端半导体研发成本。半导体行业的不同行业基于各自的优势,在不同的地区进行实现了本地化。

价值最高的行业,尤其是SEM、晶圆厂和芯片设计行业,其成本增长和整合的速度特别快。半导体制造设备成本(11%)和每个芯片的设计成本(24%)的年增长率都高于半导体市场(7%)。而半导体研发人员的数量则又以每年7%的速度增长。

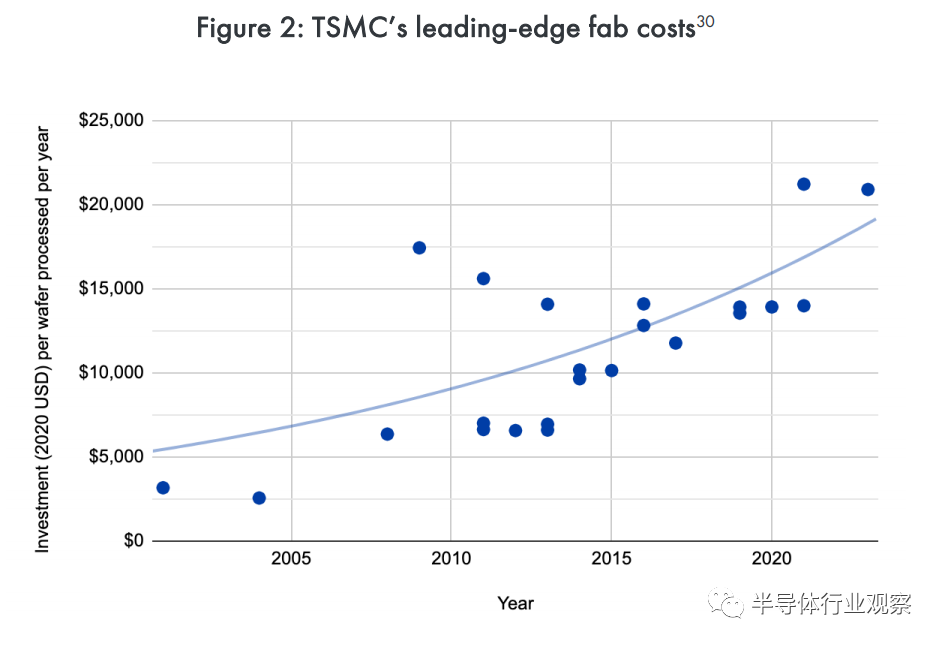

自本世纪初以来,半导体制造成本(包括晶圆厂和SEM)的年增长率一直保持在11%。固定成本的增长速度快于可变成本,这造成了更高的壁垒,挤压了晶圆厂的利润,并导致致力于先进节点的晶圆厂代工厂数量的正在减少。图2显示台积电(TSMC)在晶圆厂的建造上投入的成本增加最大。目前,在5纳米节点上只有两家芯片制造商:台湾的台积电(TSMC)和韩国的三星(Samsung)。英特尔紧随其后,计划推出7和5纳米节点;GlobalFoundries和中芯国际(SMIC)则推出了14纳米(见表1)。

图2 台积电先进节点的晶圆厂成本

光刻机是众多半导体设备当中最昂贵和最复杂的部分,其成本已从1979年的45万美元/件上升到2019年的1.23亿美元/件。目前只有荷兰的ASML光刻公司能够制造最小5纳米晶体管的光刻设备。除此之外,尼康在日本是唯一可生产大量的光刻机的企业,其出售的设备使用于≤90纳米的制程工艺上(见表1)。最终,在先进节点上增加光刻设备和晶圆厂的研发成本的企业,可以从缓慢增长的全球半导体市场收回成本。

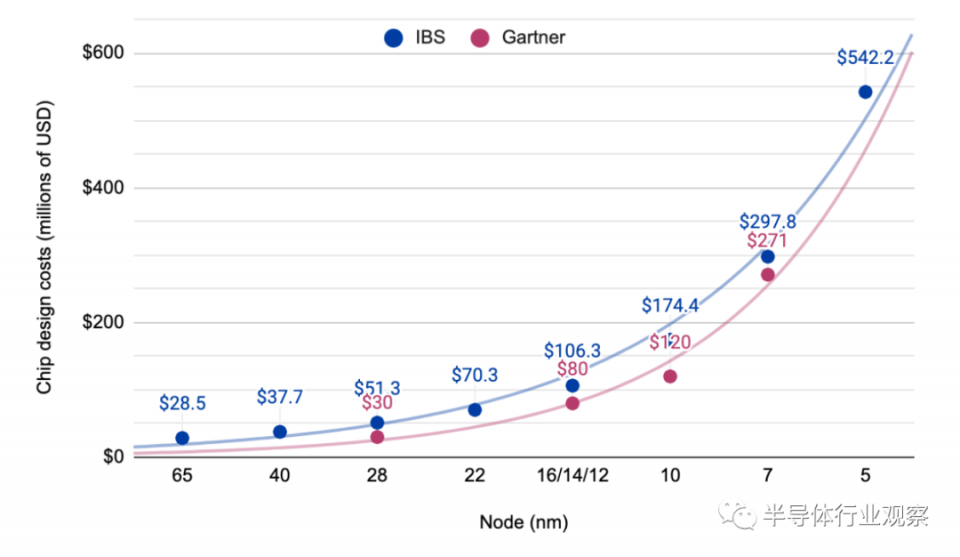

同时,如图3所示,多项估计表明芯片设计成本呈指数级上升。当与台积电的节点引入日期相匹配时,根据国际商业策略(IBS),每个节点的设计成本每年增加24%。由于它们的通用用途,CPU具有规模经济优势,使美国公司Intel和AMD能够在服务器和台式机和笔记本电脑等个人电脑(PC)的CPU设计方面保持长达数十年的双寡头垄断地位。

图3 每个节点的芯片设计成本

随着半导体复杂性的增加,对高端人才的需求推动了设计和制造成本的超支。通过将半导体研发支出除以高技能工人的工资来衡量,研究人员的有效人数从1971年到2015年增长了18倍。换言之,摩尔定律要求2015年的人类研究工作量是1971年的18倍,每年增长7%。

每个晶体管的总体设计和制造成本可能是衡量晶体管密度改进是否经济的最佳指标。这个成本在历史上每年下降了20-30%左右。一些分析师称,这种下降已经超过了2011年引入的28nm节点,而其他人则不同意。

半导体市场的增长速度已经超过了世界经济的3%。目前,半导体行业占全球经济产出的0.5%。部分由于美国和中国之间的贸易战争,半导体市场在2019年缩水,然而,它典型地呈现出逐年锯齿状的增长轨迹,因此多年的放缓更能表明长期增长的放缓。

每个节点的芯片生产

鉴于芯片生产的技术和经济挑战,新节点的引入比过去更慢。摩尔定律的标准承担者英特尔确实减慢了节点的引入。台积电在其前任产品推出两年后推出了32和22 nm节点,这与摩尔定律保持一致,但在22 nm推出三年后又推出了14 nm,而14 nm节点芯片之后又推出了10 nm。然而,领先的代工服务供应商台积电(TSMC)并没有放缓节点的推出。

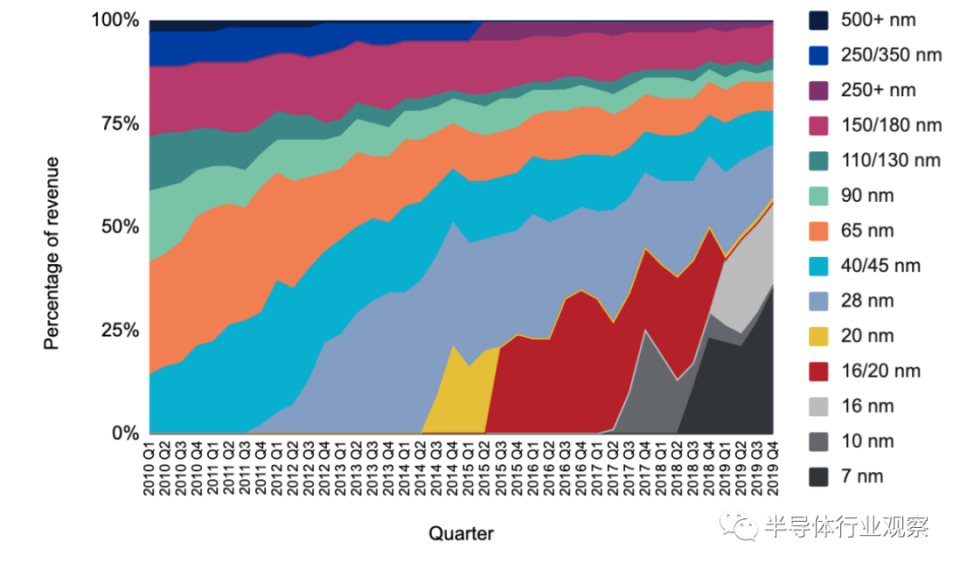

领先的节点芯片销量的趋势并不意味着新节点的采用会大幅放缓。从2002年到2016年,台积电的领先节点稳定地代表了其约20%的收入。2016年和2018年分别引入的台积电10nm和7nm节点也分别达到了25%和35%,如图4所示。

台积电新节点的稳定销售率(尽管比2000年代初期要慢)可能掩盖了整个代工服务市场正在减缓采用这一事实。在过去的十年中,台积电控制了全球约一半的晶圆代工市场份额。生产成本的上升正在减少领先节点的公司数量。例如,在此期间,Global Foundries因无法前进到14 nm以上而退出。如果这种趋势伴随着当前领先节点的晶圆厂产能低于以前领先节点的晶圆厂产能,则表明摩尔定律正在放缓。

图4 TSMC引入和采用新节点的速度保持稳定

出于几个原因,晶圆厂仍然在图4所示的旧节点上制造芯片。晶圆厂在建造领先晶圆厂或将旧晶圆厂升级为在较新节点制造晶片时,会产生巨大成本,因此不可能立即将世界晶圆厂产能转移至领先节点。相反,工厂继续以较低的价格出售旧节点,特别是向以购买成本为主要标准的客户出售旧节点。其中许多客户可能不太关心效率,因为他们的应用程序不是计算密集型的。类似地,它们的应用程序可能不需要很快的速度,或者在旧芯片上以足够快的速度完成计算。此外,一些专门的低容量产品(如模拟芯片)需要后续节点来保持成本效益。

摩尔定律变慢时芯片的改进

随着摩尔定律(Moore’s Law)的放缓,芯片在两方面继续改进:一是更小晶体管的效率和速度的提高,二是利用更小晶体管尺寸所支持的更大数量晶体管的先进芯片设计的效率和速度的提高。这些先进的设计包括在一个芯片上封装更专业的核心的能力。

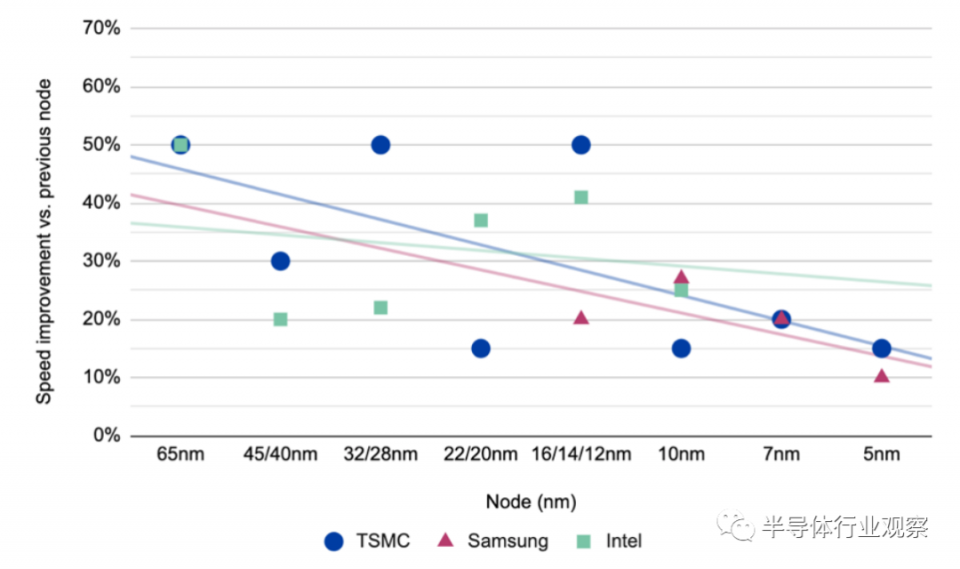

幸运的是,一些速度和效率的改进仍然是可用的,但是有相当大的技术挑战。大约在2004年,当达到65nm节点时,晶体管密度的改善在降低晶体管功耗和提高晶体管开关速度(频率缩放)方面变慢。尽管如此,晶圆厂报告称,晶体管级别的创新,而非设计级别的创新,将继续提供节点与节点之间一致(尽管速度较慢)的改进。

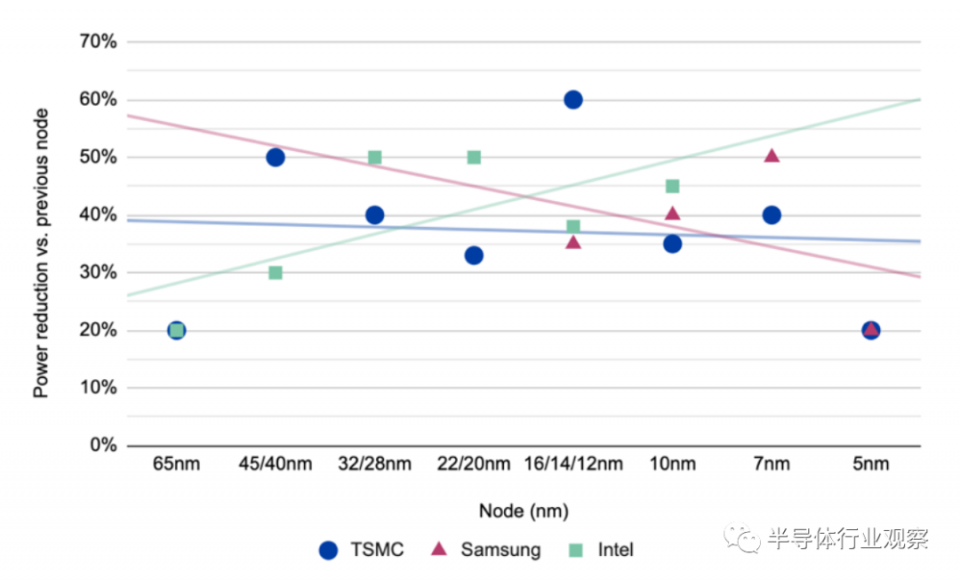

台积电和三星声称,他们的5nm节点芯片在功率保持不变的情况下,其7nm节点芯片的晶体管速度分别提高了15%和10%,而在晶体管速度保持不变的情况下,其功耗降低了30%和20%。图5和图6显示了台积电所声称的在90nm和5nm之间的恒定效率下的节点到节点晶体管速度改善的下降趋势,但是在台积电所声称的晶体管功率降低改善的下降趋势是平缓的。

图5 节点到节点晶体管速度的改进

三星在两项指标上的数据都在14nm到5nm之间呈下降趋势,但是我们缺少大于14nm的节点的数据。英特尔发现晶体管的速度略有下降,但从65nm到10nm,节点到节点的晶体管功率降低的改进仍在继续。英特尔还没有推出其7nm节点。这些速度和效率的提高既有利于像CPU这样的通用芯片,也有利于像AI芯片这样的专用芯片。

图6 节点到节点晶体管功率降低的改进

芯片设计的改进现在提供了降低CPU效率和速度的改进。图7按节点合并了CPU和晶体管的速度和效率测量。对于CPU,我们使用图1中的数据。对于晶体管,我们使用来自图5和图6的台积电和英特尔节点的数据。这些消息来源在速度和效率改进方面大致一致。台积电和英特尔报告的来自晶体管级创新的改进,通常与来自晶体管级和设计级创新的CPU改进相匹配。粗略的匹配表明,晶体管级的创新在过去15年里一直在CPU效率和速度改进方面发挥着重要作用,至少在经过测量的CPU基准测试中是这样。然而,高效的设计仍然发挥着作用。

图7 针对90 nm节点测得的效率和速度改进

改进的晶体管密度可实现专业化

除了改善晶体管功能外,增加晶体管密度还能使芯片包含更多种类的专用电路,用于执行不同类型的计算。一个芯片可以调用不同的专用电路,这取决于所请求的计算。这些电路可以包括一些优化的AI算法和其他专门针对不同类型的计算。

除了使用这些专用电路外,近年来在通用芯片上增加更多的晶体管几乎没有什么好处。从理论上讲,更多的晶体管可以使CPU包含更多的电路,从而并行执行更多的计算。然而,并行性的加速通常受到串行计算时间百分比的限制,串行计算一个接一个地执行,因为一个计算的结果需要启动另一个计算。相反,并行计算是同时进行的。即使只有1%的算法计算时间需要串行计算,也会浪费45%的处理器能量。不幸的是,大多数应用程序至少需要一些串行计算,并且随着串行化百分比的增加,处理器的能量浪费变得过高。自2000年中期以来,随着其他设计改进的放缓,拥有越来越多核心的多核设计开始激增。但是多核设计也不能有效地并行化算法,这需要在串行计算上花费大量的时间。

金大立免费服务热线

金大立免费服务热线 地址:成都彭州市工业开发区天彭镇旌旗西路419号

地址:成都彭州市工业开发区天彭镇旌旗西路419号二维码